Es gab eine Zeit, in der Computer so groß waren, dass für ihre Installation leicht ein Raum erforderlich war. Aber heute sind sie so weiterentwickelt, dass wir sie sogar problemlos als Notizbücher tragen können. Die Innovation, die dies ermöglichte, war das Konzept der integrierten Schaltkreise. Im Integrierte Schaltkreise , eine große Anzahl von aktiven und passive Elemente zusammen mit ihren Verbindungen werden über einen kleinen Siliziumwafer entwickelt, der typischerweise einen Querschnitt von 50 mal 50 mil aufweist. Die grundlegenden Verfahren, die zur Herstellung solcher Schaltungen befolgt werden, umfassen epitaktisches Wachstum, maskierte Verunreinigungsdiffusion, Oxidwachstum und Oxidätzen unter Verwendung von Photolithographie zur Herstellung eines Musters.

Zu den Komponenten über dem Wafer gehören Widerstände, Transistoren, Dioden, Kondensatoren usw. Das komplizierteste Element, das über ICs hergestellt werden kann, sind Transistoren. Es gibt verschiedene Arten von Transistoren wie CMOS, BJT, FET. Wir wählen den Typ der Transistortechnologie, die über einen IC implementiert werden soll, basierend auf den Anforderungen. In diesem Artikel machen wir uns mit dem Konzept von vertraut CMOS-Herstellung (oder) Herstellung von Transistoren als CMOS.

CMOS-Herstellung

Für weniger Verlustleistung CMOS-Technologie wird zur Implementierung von Transistoren verwendet. Wenn wir eine schnellere Schaltung benötigen, werden Transistoren über implementiert IC mit BJT . Herstellung von CMOS-Transistoren als ICs können auf drei verschiedene Arten durchgeführt werden.

Die N-Well / P-Well-Technologie, bei der die Diffusion vom n-Typ über ein Substrat vom p-Typ oder die Diffusion vom p-Typ über ein Substrat vom n-Typ erfolgt.

Das Twin-Well-Technologie , wo NMOS und PMOS-Transistor werden über dem Wafer durch gleichzeitige Diffusion über eine epitaktische Wachstumsbasis anstelle eines Substrats entwickelt.

Der Silizium-auf-Isolator-Prozess, bei dem anstelle von Silizium als Substrat ein Isolatormaterial verwendet wird, um die Geschwindigkeit und die Anfälligkeit für das Einrasten zu verbessern.

N-Well / P-Well-Technologie

CMOS kann durch Integration beider erhalten werden NMOS- und PMOS-Transistoren über den gleichen Siliziumwafer. In der N-Well-Technologie wird ein n-Well auf einem p-Substrat diffundiert, während es in der P-Well umgekehrt ist.

CMOS-Herstellungsschritte

Das CMOS-Herstellungsprozess fließen wird unter Verwendung von zwanzig grundlegenden Herstellungsschritten durchgeführt, während es unter Verwendung der N-Well / P-Well-Technologie hergestellt wird.

Herstellung von CMOS mit N gut

Schritt 1: Zuerst wählen wir ein Substrat als Basis für die Herstellung. Für N-Well wird ein Siliziumsubstrat vom P-Typ ausgewählt.

Substrat

Schritt 2 - Oxidation: Die selektive Diffusion von Verunreinigungen vom n-Typ wird unter Verwendung von SiO 2 als Barriere erreicht, die Teile des Wafers vor Verunreinigung des Substrats schützt. SiOzweiwird durch einen Oxidationsprozess ausgelegt, bei dem das Substrat in einer Oxidationskammer bei ungefähr 1000 Sauerstoff und Wasserstoff hoher Qualität ausgesetzt wird0c

Oxidation

Schritt 3 - Wachstum des Fotolacks: In diesem Stadium wird die SiO 2 -Schicht dem Photolithographieprozess unterzogen, um das selektive Ätzen zu ermöglichen. Bei diesem Verfahren wird der Wafer mit einem gleichmäßigen Film einer lichtempfindlichen Emulsion beschichtet.

Wachstum von Fotolack

Schritt 4 - Maskieren: Dieser Schritt ist die Fortsetzung des Fotolithografieprozesses. In diesem Schritt wird unter Verwendung einer Schablone ein gewünschtes Muster der Offenheit hergestellt. Diese Schablone wird als Maske über dem Fotolack verwendet. Das Substrat ist nun ausgesetzt UV-Strahlen Der unter den belichteten Bereichen der Maske vorhandene Fotolack wird polymerisiert.

Maskierung des Fotolacks

Schritt 5 - Entfernen von nicht belichtetem Fotolack: Die Maske wird entfernt und der unbelichtete Bereich des Fotolacks wird durch Entwickeln eines Wafers unter Verwendung einer Chemikalie wie Trichlorethylen gelöst.

Entfernung des Fotolacks

Schritt 6 - Radierung: Der Wafer wird in eine Ätzlösung von Flusssäure getaucht, die das Oxid aus den Bereichen entfernt, durch die Dotierstoffe diffundiert werden sollen.

Ätzen von SiO2

Schritt 7 - Entfernen der gesamten Fotolackschicht: Während der Ätzprozess Die Teile von SiO 2, die durch die Fotolackschicht geschützt sind, sind nicht betroffen. Die Fotolackmaske wird nun mit einem chemischen Lösungsmittel (heißes H2SO4) abgestreift.

Entfernen der Fotolackschicht

Schritt 8 - Bildung der N-Vertiefung: Die Verunreinigungen vom n-Typ werden durch den exponierten Bereich in das p-Typ-Substrat diffundiert, wodurch eine N-Vertiefung gebildet wird.

Bildung von N-Well

Schritt 9 - Entfernung von SiO2: Die SiO2-Schicht wird nun mit Flusssäure entfernt.

Entfernung von SiO2

Schritt 10 - Abscheidung von Polysilicium: Die Fehlausrichtung des Tores von a CMOS-Transistor würde zu unerwünschter Kapazität führen, die den Stromkreis beschädigen könnte. Um diesen 'selbstausgerichteten Gate-Prozess' zu verhindern, wird bevorzugt, dass Gate-Bereiche vor der Bildung von Source und Drain mittels Ionenimplantation gebildet werden.

Abscheidung von Polysilicium

Polysilicium wird zur Bildung des Gates verwendet, da es der hohen Temperatur von mehr als 8000 standhalten kann0c wenn ein Wafer Glühverfahren zur Bildung von Source und Drain unterzogen wird. Polysilicium wird unter Verwendung von abgeschieden Chemischer Abscheidungsprozess über einer dünnen Schicht Gateoxid. Dieses dünne Gateoxid unter der Polysiliciumschicht verhindert eine weitere Dotierung unter dem Gatebereich.

Schritt 11 - Bildung der Torregion: Mit Ausnahme der beiden für die Bildung des Tors erforderlichen Bereiche für NMOS- und PMOS-Transistoren Der verbleibende Teil von Polysilicium wird abgestreift.

Bildung der Torregion

Schritt 12 - Oxidationsprozess: Über dem Wafer wird eine Oxidationsschicht abgeschieden, die als Abschirmung für weitere dient Diffusions- und Metallisierungsprozesse .

Oxidationsprozess

Schritt 13 - Maskierung und Diffusion: Zur Herstellung von Bereichen zur Diffusion von Verunreinigungen vom n-Typ unter Verwendung eines Maskierungsverfahrens werden kleine Lücken hergestellt.

Maskierung

Unter Verwendung des Diffusionsprozesses werden drei n + Regionen für die Bildung von Terminals von NMOS entwickelt.

N-Diffusion

Schritt 14 - Entfernung von Oxid: Die Oxidschicht wird abgestreift.

Entfernung von Oxid

Schritt 15 - Diffusion vom P-Typ: Ähnlich wie bei der Diffusion vom n-Typ zur Bildung der Anschlüsse wird eine Diffusion vom PMOS-p-Typ durchgeführt.

P-Typ-Diffusion

Schritt 16 - Verlegen von Dickfeldoxid: Vor dem Formen der Metallanschlüsse wird ein dickes Feldoxid ausgelegt, um eine Schutzschicht für die Bereiche des Wafers zu bilden, in denen keine Anschlüsse erforderlich sind.

Dickfeldoxidschicht

Schritt 17 - Metallisierung: Dieser Schritt wird zur Bildung von Metallanschlüssen verwendet, die Verbindungen herstellen können. Aluminium wird auf dem gesamten Wafer verteilt.

Metallisierung

Schritt 18 - Entfernen von überschüssigem Metall: Das überschüssige Metall wird vom Wafer entfernt.

Schritt 19 - Bildung von Terminals: In den nach dem Entfernen von überschüssigen Metallklemmen gebildeten Lücken werden Klemmen für die Verbindungen gebildet.

Bildung von Terminals

Schritt 20 - Zuweisen der Terminalnamen: Namen werden den Terminals von zugewiesen NMOS- und PMOS-Transistoren .

Terminalnamen zuweisen

Herstellung von CMOS mit P-Well-Technologie

Der p-Well-Prozess ist dem N-Well-Prozess ähnlich, außer dass hier ein Substrat vom n-Typ verwendet wird und Diffusionen vom p-Typ durchgeführt werden. Der Einfachheit halber wird üblicherweise ein N-Well-Verfahren bevorzugt.

Doppelrohrherstellung von CMOS

Mit dem Doppelrohrverfahren kann die Verstärkung von Geräten vom Typ P und N gesteuert werden. Verschiedene Schritte in der Herstellung von CMOS mit der Doppelrohrmethode sind wie folgt

- Ein leicht dotiertes Substrat vom n- oder p-Typ wird genommen und die Epitaxieschicht wird verwendet. Die Epitaxieschicht schützt das Latch-Up-Problem im Chip.

- Die hochreinen Siliziumschichten mit gemessener Dicke und exakter Dotierstoffkonzentration werden gezüchtet.

- Rohrbildung für P- und N-Well.

- Dünne Oxidkonstruktion zum Schutz vor Verunreinigungen bei Diffusionsprozessen.

- Source und Drain werden unter Verwendung von Ionenimplantationsmethoden gebildet.

- Schnitte werden hergestellt, um Teile für Metallkontakte herzustellen.

- Die Metallisierung erfolgt zum Zeichnen von Metallkontakten

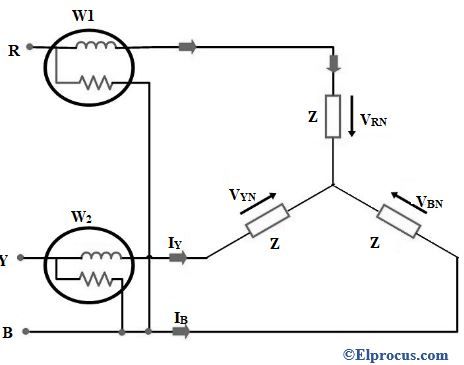

CMOS-IC-Layout

Die obere Ansicht von zu CMOS Herstellung und Layout gegeben ist. Hier können verschiedene Metallkontakte und N-Well-Diffusionen deutlich gesehen werden.

CMOS-IC-Layout

Das ist also alles über CMOS-Herstellungstechniken . Betrachten wir einen 1-in-Quadrat-Wafer, der in 400 Chips mit einer Oberfläche von 50 mil mal 50 mil unterteilt ist. Die Herstellung eines Transistors dauert 50 mil2. Daher enthält jeder IC 2 Transistoren, so dass auf jedem Wafer 2 x 400 = 800 Transistoren aufgebaut sind. Wenn pro Charge 10 Wafer verarbeitet werden, können 8000 Transistoren gleichzeitig hergestellt werden. Welche verschiedenen Komponenten haben Sie auf einem IC beobachtet?