Die ARM (Advanced RISC Machine) hat mehrere Prozessoren mit unterschiedlichen Funktionen sowie unterschiedlichen Kernen für eine Vielzahl von Anwendungen auf den Markt gebracht. Das erste ARM-Architekturdesign verfügt über 26-Bit-Prozessoren, jetzt jedoch über 64-Bit-Prozessoren. Die allgemeine Erweiterung von ARM-Produkten kann nicht in bestimmte Informationen eingeteilt werden. ARM-Produkte können jedoch anhand ihrer Architektur verstanden werden. Die auf dem Markt erhältlichen Standardprozessoren der ARM-Serie reichen von ARM7 bis ARM11. Diese Prozessoren verfügen über verschiedene Funktionen wie Cache, Data Tightly Coupled Memory, MPU, MMU usw. Einige der weithin bekannten ARM-Prozessorserien sind ARM926EJ-S, ARM7TDMI und ARM11 MPCore. Dieser Artikel ist speziell für die ARM7-basierte LPC2148-Mikrocontroller-Architekturübersicht gedacht, über die Sie kurze Informationen erhalten der Mikrocontroller die Architektur.

ARM7-basierte LPC2148-Mikrocontroller-Architektur

Das ARM7 ist ein 32-Bit-Allzweckgerät Mikroprozessor und es bietet einige der Funktionen wie geringe Stromauslastung und hohe Leistung. Die Architektur eines ARM hängt von der ab Prinzipien des RISC . Der zugehörige Dekodierungsmechanismus sowie der RISC-Befehlssatz sind im Vergleich sehr einfach mikroprogrammiertes CISC -Komplexe Befehlssatz-Computer.

Die Pipeline-Methode wird zum Verarbeiten aller Blöcke in der Architektur verwendet. Im Allgemeinen wird ein einzelner Befehlssatz ausgeführt, dann wird sein Nachkomme übersetzt, & a 3rd-Anweisung wird aus dem Speicher erhalten.

Ein exklusiver Architekturplan von ARM7 wird als Thumb bezeichnet und eignet sich perfekt für Anwendungen mit hohem Volumen, bei denen es auf die Kompaktheit des Codes ankommt. Das ARM7 verwendet auch eine exklusive Architektur, nämlich Thumb. Es ist aufgrund von Speicherbeschränkungen, bei denen die Codedichte eine Rolle spielt, perfekt für verschiedene Anwendungen geeignet.

ARM7-basierte Mikrocontroller-Architektur (LPC2148)

Quellen unterbrechen

Jedes Peripheriegerät besteht aus einer einzelnen Interrupt-Leitung, die mit dem VIC (Vector Interrupt Controller) verbunden ist, obwohl es verschiedene Interrupt-Flags enthalten kann. Einzelne Interrupt-Flags können auch eine oder mehrere Interrupt-Ressourcen kennzeichnen.

On-Chip-Flash-Programmspeicher

Der Mikrocontroller LPC2141 / 42/44/46/48 enthält einen Flash-Speicher wie 32 Kilobyte, Kilobyte, 128 Kilobyte bzw. 256 Kilobyte. Dieser Flash-Speicher kann sowohl für die Datenspeicherung als auch für den Code verwendet werden. Die Flash-Speicherprogrammierung kann im System über die serielle Schnittstelle erfolgen.

Die Programmanwendung kann auch gelöscht werden, während die Anwendung des Programms ausgeführt wird, was Flexibilität bei der Verbesserung der Firmware des Datenspeicherfelds usw. ermöglicht. Aufgrund der Auswahl einer Architekturlösung für einen On-Chip-Bootloader steht der verfügbare Speicher für die Mikrocontroller LPC2141 / 42 zur Verfügung / 44/46/48 ist 32 Kilobyte, Kilobyte, 128 Kilobyte, 256 Kilobyte und 500 Kilobyte. Der Flash-Speicher dieser Mikrocontroller bietet 1 000 000 Löschvorgänge pro Zyklus und Datenerhaltung für viele Jahre.

Pin Connect Block

Dieser Block ermöglicht ausgewählten Pins des ARM7-basierten LPC2148-Mikrocontrollers mehrere Funktionen. Die Multiplexer kann durch die Konfigurationsregister gesteuert werden, um die Verbindung zwischen dem Pin und den On-Chip-Peripheriegeräten zu ermöglichen.

Peripheriegeräte müssen vor dem Auslösen und vor dem Zulassen verbundener Interrupts mit den geeigneten Pins gekoppelt werden. Die Mikrocontroller-Funktionalität kann vom Pin-Steuermodul durch seine Pin-Auswahl von Registern in einer bestimmten Hardware-Umgebung definiert werden.

Nach dem Neuanordnen werden alle Pins der Ports (Port 0 und Port 1) gemäß den angegebenen Ausnahmen als I / P angeordnet. Wenn Debug erlaubt ist

Wenn das Debuggen zulässig ist, erraten die Pins des JTAG die Funktionalität des JTAG. Wenn eine Ablaufverfolgung zulässig ist, erraten die Ablaufverfolgungsstifte die Funktionalität der Ablaufverfolgung. Die an die I2C0- und I2C1-Pins angeschlossenen Pins sind offene Abflüsse.

GPIO - Allgemeine parallele Ein- / Ausgabe

GPIO-Register steuern die Gerätepins, die nicht mit einer bestimmten Peripheriefunktion verbunden sind. Die Gerätepins können als i / p [s oder o / ps angeordnet werden. Einzelne Register ermöglichen das gleichzeitige Löschen einer beliebigen Anzahl von O / Ps. Der Ausgangsregisterwert kann zurückgelesen werden und der aktuelle Zustand der Port-Pins. Diese Mikrocontroller beginnen eine beschleunigte Funktion über LPC200-Geräte.

Allzweck-Eingangs- / Ausgangsregister werden auf den Prozessorbus verschoben, der für die bestmögliche E / A-Zeit verwendet wird.

- Diese Register sind adressierbare Bytes.

- Der Gesamtwert eines Ports kann sein

- Der vollständige Wert des Ports kann in die einzige Anweisung geschrieben werden

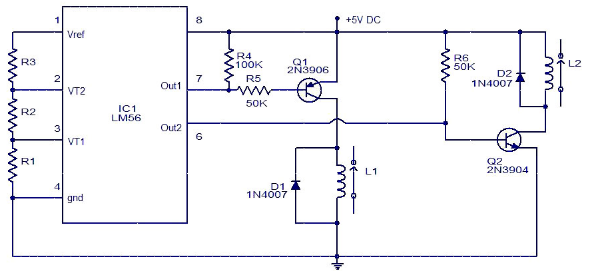

10-Bit-ADC (Analog-Digital-Wandler)

Die Mikrocontroller wie LPC2141 oder 42 umfassen zwei ADC-Wandler , und dies sind nur 10-Bit-ADCs und der LPC2144 / 46/48 hat zwei ADCs, und dies sind nur 10-Bit-ADCs mit gerader Approximation. Obwohl ADC0 6 Kanäle enthält und ADC1 8 Kanäle hat. Somit beträgt die Anzahl der zugänglichen ADC i / ps für LPC2141 oder 42 6 und 14 für LPC2141 oder 42.

10-Bit-DAC (Digital-Analog-Wandler)

Der DAC ermöglicht diesen Mikrocontrollern, ein veränderbares analoges O / P und V zu erzeugenREFist die äußerste Ausgabe von a digital zu einem analogen Stromspannung.

Gerätesteuerung-USB 2.0

Der universelle serielle Bus besteht aus 4 Drähten und unterstützt die Kommunikation zwischen einer Reihe von Peripheriegeräten und Hosts. Dieser Controller ermöglicht die USB-Bandbreite zum Verbinden von Geräten mithilfe eines auf dem Token basierenden Protokolls.

Der Bus unterstützt das Herausziehen des Hotplugs und die dynamische Erfassung der Geräte. Jede Kommunikation wird über den Host-Controller gestartet. Diese Mikrocontroller sind mit einem universellen seriellen Busapparat-Controller ausgestattet, mit dem 12-Mbit / s-Daten durch einen USB-Host-Controller ersetzt werden können.

UARTs

Diese Mikrocontroller enthalten zwei UARTs für Standard-Sende- und Abrufdatenleitungen. Im Gegensatz zu früheren Mikrocontrollern (LPC2000) initiieren UARTs in den Mikrocontrollern LPC2141 / LPC2142 / LPC2144 / LPC2146 / LPC2148 einen partiellen Baudratengenerator, der für beide UARTs verwendet wird, wodurch diese Arten von Mikrocontrollern typische Baudraten wie 115200 für jede Kristallfrequenz über 2 MHz erreichen können . Zusätzlich werden die Steuerfunktionen wie CTS / RTS vollständig in Hardware ausgeführt.

Serieller E / A-Controller des I2C-Busses

Jeder Mikrocontroller von LPC2141 / LPC2142 / LPC2144 / LPC2146 / LPC2148 enthält zwei I2C Bussteuerungen, und dies ist bidirektional. Die Inter-IC-Steuerung kann mit Hilfe von zwei Drähten erfolgen, nämlich einer SCL und einer SDA. Hier sind SDA & SCL serielle Taktleitung und serielle Datenleitung

Jedes Gerät ist durch eine individuelle Adresse gekennzeichnet. Hier können Sender und Empfänger in zwei Modi wie Master-Modus / Slave-Modus arbeiten. Dies ist ein Multi-Master-Bus, der von einem oder mehreren damit verbundenen Busmastern verwaltet werden kann. Diese Mikrocontroller unterstützen Bitraten von bis zu 400 kbit / s.

SPI Serial Input / Output Controller

Diese Mikrocontroller enthalten einen einzelnen SPI-Controller und sind für die Verarbeitung zahlreicher Master und Slaves vorgesehen, die einem bestimmten Bus zugeordnet sind.

Einfach ein Master und ein Slave können sich während der angegebenen Datenübertragung über die Schnittstelle unterhalten. Währenddessen überträgt der Master ständig ein Datenbyte an den Slave, und der Slave überträgt ständig Daten an den Master.

SSP Serial Input / Output Controller

Diese Mikrocontroller enthalten einen einzelnen SSP, und dieser Controller kann auf einem SPI, einem Microwire-Bus oder einem 4-Draht-SSI verarbeitet werden. Es kann mit dem Bus mehrerer Master sowie Slaves kommunizieren

Aber einfach ein bestimmter Master sowie ein Slave können sich während einer bestimmten Datenübertragung auf dem Bus unterhalten. Dieser Mikrocontroller unterstützt Vollduplex-Übertragungen mit 4-16-Bit-Datenrahmen, die für den Datenfluss vom Master - dem Slave - sowie vom Slave - dem Master - verwendet werden.

Timer / Zähler

Timer und Zähler sind zum Zählen der PCLK-Zyklen (Peripherietakt) ausgelegt und erzeugen optional Interrupts basierend auf 4-Match-Registern.

Und es umfasst vier Erfassungs-I / Ps, um den Wert eines Timers zu erfassen, wenn sich ein I / P-Signal ändert. Es können mehrere Pins ausgewählt werden, um eine bestimmte Erfassung auszuführen. Diese Mikrocontroller können äußere Ereignisse an den Eingängen der Erfassung berechnen, wenn der kleinste äußere Impuls äquivalent ist. In dieser Anordnung können Leerlauferfassungsleitungen als übliche Zeitgebererfassungs-i / ps ausgewählt werden.

Watchdog Timer

Der Watchdog-Timer wird verwendet, um den Mikrocontroller in angemessener Zeit zurückzusetzen. Wenn dies zulässig ist, führt der Timer einen Reset eines Systems durch, wenn es dem Verbraucherprogramm nicht gelingt, den Timer in einer festgelegten Zeitspanne neu zu laden.

RTC-Echtzeituhr

Die RTC dient zur Bereitstellung von Zählern zur Berechnung der Zeit, zu der die Leerlauf- oder normale Betriebsmethode gewählt wird. Die RTC verbraucht wenig Strom und ist für geeignete batteriebetriebene Anordnungen ausgelegt, bei denen die Zentraleinheit nicht ständig funktioniert

Stromschalter

Diese Mikrocontroller unterstützen zwei kondensierte Leistungsmodi wie den Abschaltmodus und den Leerlaufmodus. Im Leerlaufmodus wird die Befehlsausführung ausgeglichen, bis ein Interrupt oder RST auftritt. Die Funktionen des Peripheriegeräts behalten den Betrieb während des Leerlaufmodus bei und können Interrupts erzeugen, die dazu führen, dass die CPU die Endbearbeitung neu startet. Im Leerlaufmodus wird die von der CPU, den Controllern, den Speichersystemen und den inneren Bussen verbrauchte Energie entfernt.

Im Power-Down-Modus ist der Oszillator deaktiviert und der IC erhält keine inneren Takte. Die Peripherieregister, der Prozessorzustand mit Registern und die inneren SRAM-Werte bleiben während des Abschaltmodus erhalten und die Ausgangspins der Chiplogikpegel bleiben fest.

Dieser Modus kann beendet und der allgemeine Prozess durch bestimmte Interrupts neu gestartet werden, die ohne Uhren arbeiten können. Da der Chipbetrieb ausgeglichen ist, verringert der Power-Down-Modus die Auslastung des Chips auf nahezu Null.

PWM-Pulsweitenmodulator

Die PWMs basieren auf dem normalen Timer-Block und sind auch in allen Funktionen enthalten, obwohl einfach die Pulsweitenmodulatorfunktion auf den Mikrocontrollern wie LPC2141 / 42/44/46/48 festgelegt ist.

Der Timer soll PCLK-Zyklen (Peripherietakt) berechnen und optional Interrupts erzeugen, wenn bestimmte Timerwerte basierend auf 7-Match-Registern auftreten, und die PWM-Funktion hängt auch von Match-Register-Ereignissen ab.

Die Fähigkeit, ansteigende und abnehmende Grenzpositionen individuell zu steuern, ermöglicht es, die Pulsweitenmodulation für mehrere Anwendungen zu verwenden. Beispielsweise verwendet die typische Motorsteuerung mit Mehrphasensteuerung 3 nicht überlappende PWM-Ausgänge durch separate Steuerung aller Impulsbreiten sowie Positionen.

VPB Bus

Der VPB-Teiler löst die Zuordnung zwischen der CCLK (Prozessortakt) und der PCLK (von Peripheriegeräten verwendete Uhr) auf. Dieser Teiler wird für zwei Zwecke verwendet. Die erste Verwendung besteht darin, Peripheriegeräte über den bevorzugten PCLK unter Verwendung eines VPB-Busses zu versorgen, damit sie mit der ausgewählten Geschwindigkeit des ARM-Prozessors arbeiten können. Um dies zu erreichen, kann diese Busgeschwindigkeit die Taktrate des Prozessors von 1⁄ 2 -1⁄ 4 reduziert werden.

Da dieser Bus beim Einschalten genau arbeiten muss und der Standardzustand bei RST (Zurücksetzen) darin besteht, dass der Bus mit 1⁄ 4 der Prozessortaktrate arbeitet. Die zweite Verwendung besteht darin, Energieeinsparungen zu ermöglichen, wenn eine Anwendung keine Peripheriegeräte benötigt, um mit der vollständigen Prozessorrate zu arbeiten. Da der VPB-Teiler dem Ausgang von PLL zugeordnet ist, bleibt dieser während eines Leerlaufmodus aktiv.

Emulation & Debugging

Der Mikrocontroller (LPC2141 / 42/44/46/48) hält die Emulation und das Debuggen über den seriellen Port-JTAG aufrecht. Ein Trace-Port ermöglicht die Verfolgung der Ausführung des Programms. Trace-Funktionen und Debugging-Konzepte werden mit Port1 und GPIOs gemultiplext.

Codesicherheit

Die Codesicherheitsfunktion dieser Mikrocontroller LPC2141 / 42/44/46/48 ermöglicht es einer Funktion zu steuern, ob sie vor einer Inspektion geschützt oder debuggt werden kann.

Hier geht es also um die ARM7-basierte LPC2148-Mikrocontroller-Architektur. Aus dem obigen Artikel können wir schließlich schließen, dass ARM eine Architektur ist, die in zahlreichen Prozessoren sowie Mikrocontrollern verwendet wird. Hier ist eine Frage für Sie, wie ist die Architektur eines ARM-Prozessors?