Das Phasenregelkreis ist einer der Grundbausteine moderner elektronischer Systeme. Es wird im Allgemeinen in Multimedia, Kommunikation und in vielen anderen Anwendungen verwendet. Es gibt zwei verschiedene Arten von PLLs - lineare und nichtlineare. Das Nichtlineare ist in der realen Welt schwierig und kompliziert zu entwerfen, aber die Theorie der linearen Steuerung ist in analogen PLLs gut modelliert. Die PLL hat bewiesen, dass ein lineares Modell für die meisten elektronischen Anwendungen ausreicht.

Was ist ein Phasenregelkreis?

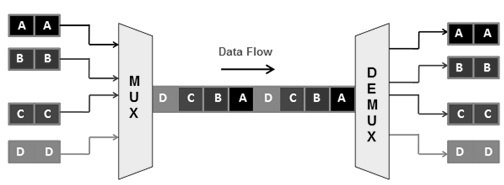

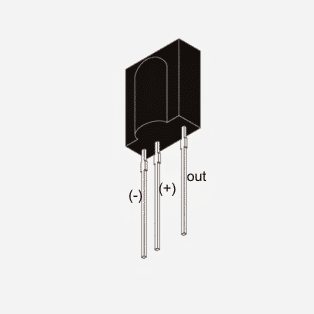

Ein Phasenregelkreis besteht aus einem Phasendetektor und einem spannungsgesteuerten Oszillator. Der Ausgang des Phasendetektors ist der Eingang des spannungsgesteuerten Oszillators (VCO), und der Ausgang des VCO ist mit einem der Eingänge eines Phasendetektors verbunden, der unten im Basisblockdiagramm gezeigt ist. Wenn diese beiden Geräte einander zugeführt werden, bildet sich die Schleife.

GRUNDDIAGRAMM DER PHASE LOCKED LOOP

Blockdiagramm und Funktionsprinzip von PLL

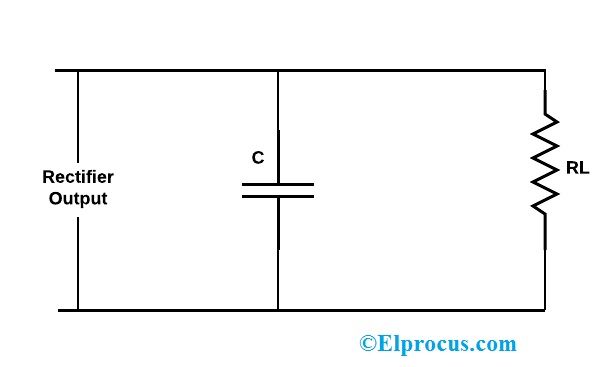

Der Phasenregelkreis besteht aus einem Phasendetektor, a spannungsgesteuerter Oszillator und dazwischen ist ein Tiefpassfilter fixiert. Das Eingangssignal 'Vi' mit der Eingangsfrequenz 'Fi' wird von einem Phasendetektor übertragen. Grundsätzlich ist der Phasendetektor ein Komparator das vergleicht die Eingangsfrequenz fi mit der Rückkopplungsfrequenz fo. Der Ausgang des Phasendetektors ist (fi + fo), was eine Gleichspannung ist. Der Detektor außerhalb des Phasendetektors, d. H. Die Gleichspannung, wird in das Tiefpassfilter (LPF) eingegeben. Er entfernt das Hochfrequenzrauschen und erzeugt einen konstanten Gleichstrompegel, d. H. Fi-Fo. Das Vf ist auch ein dynamisches Merkmal der PLL.

PLL-Blockdiagramm

Der Ausgang des Tiefpassfilters, d. H. Der Gleichstrompegel, wird an den VCO weitergeleitet. Das Eingangssignal ist direkt proportional zur Ausgangsfrequenz des VCO (fo). Die Eingangs- und Ausgangsfrequenzen werden verglichen und über die Rückkopplungsschleife eingestellt, bis die Ausgangsfrequenz gleich der Eingangsfrequenz ist. Daher funktioniert die PLL wie Freilauf, Erfassung und Phasenverriegelung.

Wenn keine Eingangsspannung angelegt wird, spricht man von einer freilaufenden Stufe. Sobald sich die an die VOC angelegte Eingangsfrequenz ändert und zum Vergleich eine Ausgangsfrequenz erzeugt, spricht man von einer Erfassungsstufe. Die folgende Abbildung zeigt das Blockdiagramm der PLL.

Phasenregelkreisdetektor

Der Phasenregelkreisdetektor vergleicht die Eingangsfrequenz und die Ausgangsfrequenz des VCO, um eine Gleichspannung zu erzeugen, die direkt proportional zur Phasendifferenzierung der beiden Frequenzen ist. Die analogen und digitalen Signale werden im Phasenregelkreis verwendet. Der größte Teil der monolithischen PLL integrierte Schaltkreise Verwenden Sie einen analogen Phasendetektor, und die meisten Phasendetektoren sind vom digitalen Typ. Eine doppelt symmetrische Mischschaltung wird üblicherweise in analogen Phasendetektoren verwendet. Einige gängige Phasendetektoren sind nachstehend aufgeführt:

Exklusiver ODER-Phasendetektor

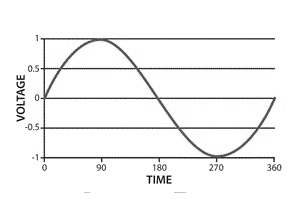

Ein exklusiver ODER-Phasendetektor ist vom Typ CMOS IC 4070. Die Eingangs- und Ausgangsfrequenzen werden an den EX OR-Phasendetektor angelegt. Um den Ausgang hoch zu erhalten, sollte mindestens ein Eingang niedrig sein und die anderen Ausgangsbedingungen sind niedrig, was in der folgenden Wahrheitstabelle gezeigt ist. Betrachten wir die Wellenform, die Eingangs- und Ausgangsfrequenzen, d. H. Fi und fo haben eine Phasendifferenz von 0 Grad. Dann ist die DC-Ausgangsspannung des Komparators eine Funktion der Phasendifferenz zwischen den beiden Eingängen.

| Sein | fo | VDC |

niedrig | niedrig | niedrig |

niedrig | hoch | hoch |

hoch | Niedrig | hoch |

Hoch | Hoch | niedrig |

Die Funktionen der Phasendifferenz zwischen fi und fo sind in der Grafik der DC-Ausgangsspannung dargestellt. Wenn der Phasendetektor 180 Grad beträgt, ist die Ausgangsspannung maximal. Wenn sowohl die Eingangs- als auch die Ausgangsfrequenz Rechteckwellen sind, werden diese Phasendetektoren verwendet.

Exklusiver ODER-Phasendetektor

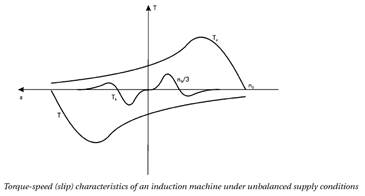

Flächentrigger-Phasendetektor

Ein Flankentrigger-Phasendetektor wird verwendet, wenn die Eingangs- und Ausgangsfrequenzen eine Impulswellenform haben, die weniger als 50% Tastverhältnis beträgt. Das R-S-Flipflop wird für die Phasendetektoren verwendet, die in der folgenden Abbildung dargestellt sind. Von R-S Flip-Flop sind die beiden NOR-Gatter kreuzgekoppelt. Der Ausgang des Phasendetektors kann seinen logischen Zustand durch Auslösen des R-S-Flipflops ändern. Die positive Flanke der Eingangs- und Ausgangsfrequenzen kann den Ausgang des Phasendetektors verändern.

Flächentrigger-Phasendetektor

Monolithischer Phasendetektor

Ein monolithischer Phasendetektor ist ein CMOS-Typ, d. H. IC 4044. Er wird stark von der Oberschwingungsempfindlichkeit kompensiert und die Tastverhältnisprobleme werden aufgegeben, da die Schaltung nur auf den Übergang des Eingangssignals reagieren kann. In kritischen Anwendungen ist es der am meisten fiebrige Phasendetektor. Die unabhängigen Variationen der Amplitude sind frei von Phasenfehler, Ausgangsfehlerspannung und Arbeitszyklus der Eingangswellenformen.

Anwendungen des Phasenregelkreises

- FM-Demodulationsnetzwerke für FM-Operationen

- Es wird in verwendet Motordrehzahlregler und Tracking-Filter.

- Es wird in Frequenzverschiebungsdecodierungen für Demodulationsträgerfrequenzen verwendet.

- Es wird rechtzeitig zu Digitalwandlern eingesetzt.

- Es wird zur Jitterreduzierung, Skew-Unterdrückung und Taktwiederherstellung verwendet.

Hier geht es um das Arbeits- und Funktionsprinzip des Phasenregelkreises und seine Anwendungen. Wir hoffen, dass die Informationen im Artikel hilfreich sind, um etwas über das Projekt zu wissen und es zu verstehen. Darüber hinaus, wenn Sie Fragen zu diesem Artikel und weiter haben elektrische und elektronische Projekte Sie können im folgenden Abschnitt kommentieren. Hier ist eine Frage an Sie, wie Sie die PLL für Stabilität am besten simulieren können.

Bildnachweis:

- Blockdiagramm der PLL Schaltung heute

- Exklusiver ODER-Phasendetektor Sanfoundry

- Flächentrigger-Phasendetektor LEARNABOUT-ELECTRONICS