Der Designprozess digitaler Hardware hat sich in den letzten Jahren stark verändert. So können kleine digitale Schaltungen mithilfe von PALs und PLAs implementiert werden. Jedes Gerät wird verwendet verschiedene Schaltungen zu implementieren Diese benötigen nicht mehr als die Anzahl der i / ps, o / ps und Produktbedingungen, die auf dem jeweiligen Chip angeboten werden. Diese Chips sind für relativ bescheidene Größen nicht geeignet und unterstützen normalerweise eine gegenseitige Anzahl von Ein- und Ausgängen von nicht mehr als 32. Zum Entwerfen dieser Schaltungen, die mehr Ein- und Ausgänge benötigen, können entweder zahlreiche PLAs / PALs oder ein klassischerer Typ verwendet werden of Chip kann als CPLD (Complex Programmable Logic Device) bezeichnet werden. Ein CPLD-Chip enthält mehrere Schaltungsblöcke auf einem einzelnen Chip mit internen Verdrahtungsressourcen zum Anbringen der Schaltungsblöcke. Jeder Schaltungsblock ist vergleichbar mit einem PLA oder einem PAL.

Was ist ein komplexes programmierbares Logikgerät?

Das Akronym der CPLD lautet „Komplexe programmierbare Logikgeräte“ Art der integrierten Schaltung dass Anwendungsentwickler digitale Hardware wie Mobiltelefone implementieren. Diese können wissentlich höhere Designs verarbeiten als SPLDs (einfache programmierbare Logikgeräte), bieten jedoch weniger Logik als FPGAs ( Feldprogrammierbare Gate-Arrays ) .CPLDs enthalten zahlreiche Logikblöcke. Jeder der Blöcke enthält 8-16 Makrozellen. Da jeder Logikblock eine bestimmte Funktion ausführt, sind alle Makrozellen in einem Logikblock vollständig verbunden. Abhängig von der Verwendung können diese Blöcke miteinander verbunden sein oder nicht.

Komplexes programmierbares Logikgerät

Die meisten CPLDs (komplexe programmierbare Logikbausteine) haben Makrozellen mit einer Summe aus Logikfunktion und Wahlfach FF (Flip-Flop) . Je nach Chip unterstützt die kombinatorische Logikfunktion 4 bis 16 Produktterme mit inklusive Fan-In. CPLDs unterscheiden sich auch in Bezug auf Schieberegister und Logikgatter. Aus diesem Grund können CPLDs mit einer großen Anzahl von Logikgattern anstelle von FPGAs verwendet werden. Eine andere CPLD-Spezifikation gibt die Anzahl der Produktbegriffe an, die eine Makrozelle ausführen kann. Produktbegriffe sind das Produkt digitaler Signale, die eine bestimmte Logikfunktion ausführen.

CPLDs sind in verschiedenen IC-Paketformen und Logikfamilien verfügbar. CPLDs unterscheiden sich auch in Bezug auf Versorgungsspannung, Betriebsstrom, Standby-Strom und Verlustleistung. Darüber hinaus sind diese mit verschiedenen Speichermengen und verschiedenen Arten von Speicherunterstützung erhältlich. Normalerweise wird der Speicher in Bit / Megabit ausgedrückt. Die Speicherunterstützung besteht aus ROM, RAM und Dual-Port-RAM. Es umfasst auch einen CAM-Speicher (Content Addressable Memory) sowie einen FIFO-Speicher (First-In, First-Out) und einen LIFO-Speicher (Last-In, Last-Out).

Architektur komplexer programmierbarer Logikgeräte

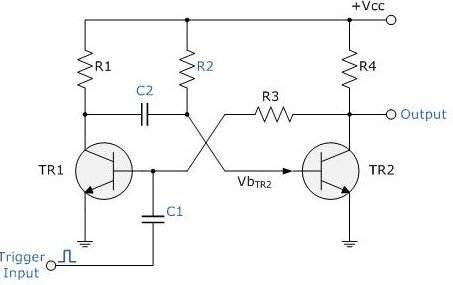

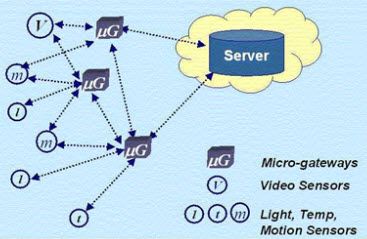

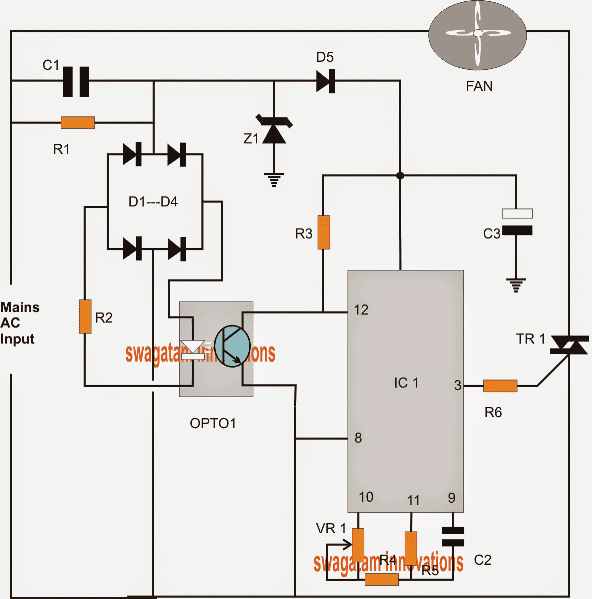

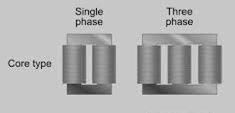

Ein komplexes programmierbares Logikgerät besteht aus einer Gruppe programmierbarer FBs (Funktionsblöcke). Die Ein- und Ausgänge dieser Funktionsblöcke sind durch eine GIM (Global Interconnection Matrix) miteinander verbunden. Diese Verbindungsmatrix ist rekonfigurierbar, so dass wir die Kontakte zwischen den Funktionsblöcken ändern können. Es wird einige Eingabe- und Ausgabeblöcke geben, mit denen wir CPLD mit der Außenwelt vereinen können. Die Architektur von CPLD ist unten dargestellt.

Im Allgemeinen sieht der programmierbare FB wie der aus Array von Logikgattern , wo ein Array von UND-Gattern programmiert werden kann und ODER-Gatter stabil sind. Jeder Hersteller hat jedoch seine eigene Denkweise, um den Funktionsblock zu entwerfen. Ein aufgelisteter O / P kann durch Betreiben der von den ODER-Gatterausgängen erhaltenen Rückkopplungssignale gefunden werden.

CPLD-Architektur

Bei der CPLD-Programmierung wird das Design zuerst in Verilog- oder VHDL-Sprache codiert, sobald der Code (simuliert und synthetisiert) ist. Während der Synthese wird das CPLD-Modell (Zielgerät) von Hand ausgewählt und eine technologiebasierte Mapping-Netzliste erstellt. Diese Liste kann geschlossen werden - Anpassung an die echte CPLD-Architektur unter Verwendung eines Orts- und Routenprozesses, der normalerweise durch die Orts- und Routensoftware der CPLD Company erreicht wird. Anschließend führt der Bediener einige Bestätigungsprozesse durch. Wenn alles in Ordnung ist, verwendet er die CPLD er wird es neu ordnen.

Architekturprobleme von CPLD

Bei der Betrachtung eines komplexen programmierbaren Logikgeräts zur Verwendung beim Entwurf können einige folgende Architekturprobleme berücksichtigt werden

- Die Programmiertechnik

- Die Funktionsblockfähigkeit

- Die E / A-Fähigkeit

Einige der CPLD-Familien verschiedener Einzelhändler sind

- Altera MAX 7000 und MAX 9000 Familien

- Atmel ATF- und ATV-Familien

- Gitter-ISP-LSI-Familie

- Gitter (Vantis) MACH Familie

- Xilinx XC9500-Familie

Familien von CPLD

Anwendungen von CPLD

Die Anwendungen von CPLDs umfassen Folgendes

- Komplexe programmierbare Logikbausteine sind ideal für leistungsstarke, kritische Steuerungsanwendungen.

- CPLD kann in digitalen Designs verwendet werden, um die Funktionen des Bootloaders auszuführen

- CPLD wird zum Laden der Konfigurationsdaten eines feldprogrammierbaren Gate-Arrays aus einem nichtflüchtigen Speicher verwendet.

- Im Allgemeinen werden diese in kleinen Entwurfsanwendungen wie der Adressdecodierung verwendet

- CPLDs werden häufig in vielen Anwendungen verwendet, beispielsweise in kostensensitiven, batteriebetriebenen tragbaren Geräten, da sie klein sind und wenig Strom verbrauchen.

Hier geht es also um die komplexe Architektur programmierbarer Logikgeräte und ihre Anwendungen. Wir hoffen, dass Sie dieses Konzept besser verstehen. Darüber hinaus Fragen zu diesem Konzept oder elektrische und elektronische Projekte umzusetzen Bitte geben Sie Ihre wertvollen Vorschläge, indem Sie im Kommentarbereich unten einen Kommentar abgeben. Hier ist eine Frage für Sie, was ist der Unterschied zwischen CPLD und FPGA?

Bildnachweis:

- CPLD Wikimedia

- Architektur der CPLD Slidesharecdn